CNET has managed to seize the primary die pictures of a number of next-generation Intel Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs which can be being examined & produced contained in the chipmaker’s Fab 42, located in Arizona, US.

Wonderful Die Pictures of Intel’s Subsequent-Gen Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs Captured at Fab 42 in Arizona

The die pictures have been captured by CNET’s Senior Reporter, Stephen Shankland, who visited Intel’s Fab 42, situated in Arizona, US. All of the magic occurs right here because the Fabrication manufacturing unit is producing next-generation chips for customers, knowledge facilities, and the high-performance computing segments. The Fab 42 will deal with Intel’s next-generation chips produced on the 10nm (Intel 7) and 7nm (Intel 4) course of nodes. A few of the key merchandise that may make the most of these next-generation nodes embody the Meteor Lake shopper processors, Sapphire Rapids Xeon processors, and Ponte Vecchio GPUs for HPC.

Intel 4 Powered Meteor Lake CPUs For Shopper Computing

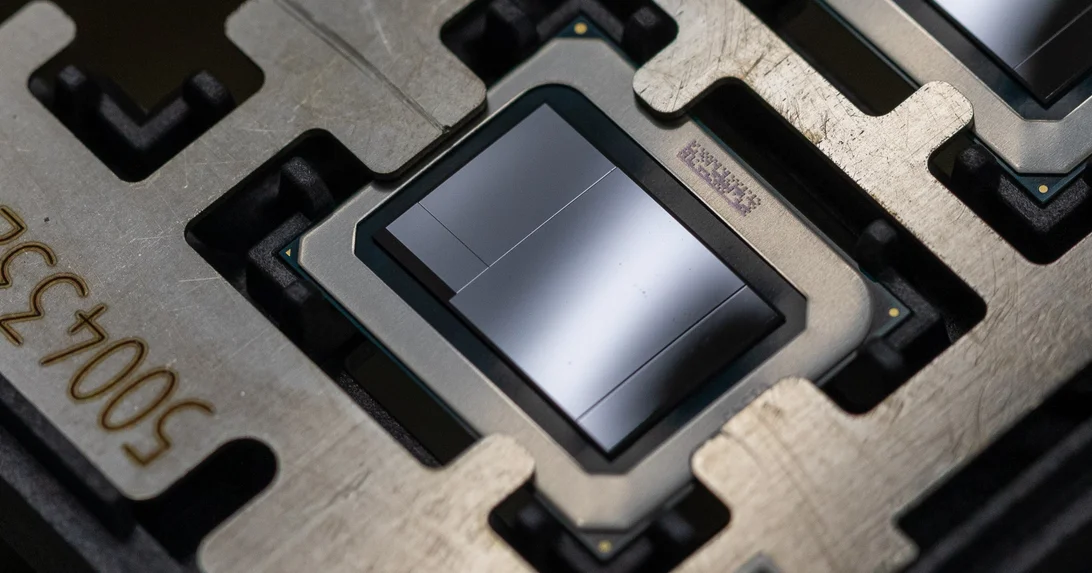

The primary product to speak about is Meteor Lake. Heading to shopper desktop PCs in 2023, the Meteor Lake CPUs would be the first true multi-chiplet design from Intel. CNET managed to get pictures of the primary Meteor Lake take a look at chips which look remarkably much like the renders that Intel teased again at their Structure Day 2023 occasion. The Meteor Lake take a look at automobile pictured above is used to make sure that the Forveros packaging design works accurately and as anticipated. Meteor Lake CPUs will make the most of Intel’s Forveros packaging know-how to interconnect the assorted core IPs built-in on the chip.

Intel Meteor Lake take a look at chips put together Chipzilla for the ultimate manufacturing of next-gen Core CPUs. (Picture Credit: CNET)

The die has 4 chiplets which can be linked collectively on the identical substrate. Based mostly on what Intel has proven of their renders, the highest die must be the Compute Tile, the center tile must be the SOC-LP tile and the lower-most die must be the GPU tile. Nevertheless, primarily based on the die sizes, that does not go alongside nicely. The center die could possibly be the principle Compute tile that homes the cores and the smaller die beneath it could possibly be the SOC-LP tile that features the IO. The topmost die must be the GPU whereas the smaller die subsequent to it could possibly be a separate cache or one other IO tile. THis is simply pure hypothesis for now as these are take a look at chips and the ultimate design might find yourself being completely different.

We additionally get a primary take a look at the Meteor Lake take a look at chip wafer which measures 300mm diagonally. The wafer contains take a look at chips that are dummy dies, as soon as once more to ensure that the interconnects on the chip work as meant. Intel already achieved Energy-On for its Meteor Lake Compute CPU tile so we will anticipate ultimate chips to be produced by the 2nd of 2023 for launch in 2023.

This is Every part We Know About The 14th Gen Meteor Lake 7nm CPUs

We already obtained some particulars from Intel comparable to the truth that Intel’s Meteor Lake line of desktop and mobility CPUs are anticipated to be primarily based on a brand new line of Cove core structure. That is rumored to be generally known as the ‘Redwood Cove’ and might be primarily based on a 7nm EUV course of node. It’s acknowledged that the Redwood Cove is designed from the bottom as much as be an agnostic node which implies that it may be fabricated at completely different fabs. There are references talked about that time out to TSMC to be a backup or perhaps a partial provider for the Redwood Cove-based chips. This may inform us why Intel is stating a number of manufacturing processes for the CPU household.

The Meteor Lake CPUs might probably be the primary CPU technology from Intel to say farewell to the ring bus interconnect structure. There are additionally rumors that Meteor Lake could possibly be a totally 3D-Stacked design and will make the most of an I/O die sourced from an exterior fab (TSMC sighted once more). It’s highlighted that Intel might be formally using its Foveros Packaging Know-how on the CPU to inter-connect the assorted dies on the chip (XPU). This additionally aligns with Intel referring to every tile on 14th Gen chips individually (Compute Tile = CPU Cores).

The Meteor Lake Desktop CPU household is anticipated to retain assist on the LGA 1700 socket which is identical socket utilized by Alder Lake & Raptor Lake processors. We are able to anticipate DDR5 reminiscence and PCIe Gen 5.0 assist. The platform will assist each DDR5 & DDR4 reminiscence with the mainstream and finances tier choices going for DDR4 reminiscence DIMMs whereas the premium & high-end choices going for DDR5 DIMMs. The location additionally lists down each Meteor Lake P and Meteor Lake M CPUs that might be aimed toward mobility platforms.

Intel Mainstream Desktop CPU Generations Comparability:

| Intel CPU Household | Processor Course of | Processors Cores/Threads (Max) | TDPs | Platform Chipset | Platform | Reminiscence Help | PCIe Help | Launch |

|---|---|---|---|---|---|---|---|---|

| Sandy Bridge (2nd Gen) | 32nm | 4/8 | 35-95W | 6-Sequence | LGA 1155 | DDR3 | PCIe Gen 2.0 | 2011 |

| Ivy Bridge (third Gen) | 22nm | 4/8 | 35-77W | 7-Sequence | LGA 1155 | DDR3 | PCIe Gen 3.0 | 2012 |

| Haswell (4th Gen) | 22nm | 4/8 | 35-84W | 8-Sequence | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2013-2014 |

| Broadwell (fifth Gen) | 14nm | 4/8 | 65-65W | 9-Sequence | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2015 |

| Skylake (sixth Gen) | 14nm | 4/8 | 35-91W | 100-Sequence | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2015 |

| Kaby Lake (seventh Gen) | 14nm | 4/8 | 35-91W | 200-Sequence | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Espresso Lake (eighth Gen) | 14nm | 6/12 | 35-95W | 300-Sequence | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Espresso Lake (ninth Gen) | 14nm | 8/16 | 35-95W | 300-Sequence | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2018 |

| Comet Lake (tenth Gen) | 14nm | 10/20 | 35-125W | 400-Sequence | LGA 1200 | DDR4 | PCIe Gen 3.0 | 2020 |

| Rocket Lake (eleventh Gen) | 14nm | 8/16 | 35-125W | 500-Sequence | LGA 1200 | DDR4 | PCIe Gen 4.0 | 2021 |

| Alder Lake (twelfth Gen) | Intel 7 | 16/24 | 35-125W | 600 Sequence | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2021 |

| Raptor Lake (thirteenth Gen) | Intel 7 | 24/32 | 35-125W | 700-Sequence | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2023 |

| Meteor Lake (14th Gen) | Intel 4 | TBA | 35-125W | 800 Sequence? | LGA 1700 | DDR5 | PCIe Gen 5.0? | 2023 |

| Arrow Lake (fifteenth Gen) | Intel 4? | 40/48 | TBA | 900-Sequence? | TBA | DDR5 | PCIe Gen 5.0? | 2024 |

| Lunar Lake (sixteenth Gen) | Intel 3? | TBA | TBA | 1000-Sequence? | TBA | DDR5 | PCIe Gen 5.0? | 2025 |

| Nova Lake (seventeenth Gen) | Intel 3? | TBA | TBA | 2000-Sequence? | TBA | DDR5? | PCIe Gen 6.0? | 2026 |

Intel 7 Powered Sapphire Rapids CPUs For Xeon Knowledge Heart & Servers

We additionally get a extra detailed take a look at the Intel Sapphire Rapids-SP Xeon CPU substrate, chiplets, and full package deal design (each normal and HBM variants). The usual variant options 4 tiles that may incorporate the compute chiplets. There are additionally 4 pin-outs for the HBM packages. The chip will talk with all 8 chiplets (4 compute / 4 HBM) by way of EMIB interconnects that are the smaller rectangular bars on the sting of every die.

A substrate of the Intel Sapphire Rapids-SP Xeon CPU with HBM2e reminiscence. (Picture Credit: CNET)

The ultimate product will be seen beneath and exhibits the 4 Xeon Compute tiles within the center with 4 smaller HBM2 packages on the edges. Intel just lately confirmed that it is Sapphire Rapids-SP Xeon CPUs will characteristic as much as 64 GB HBM2e reminiscence onboard the CPUs. That is the full-fledged CPU design proven right here and exhibits that it is prepared for deployment in next-generation knowledge facilities by 2023.

The ultimate 4th Gen Sapphire Rapids-SP Xeon CPU with its multi-chiplet design housing Compute & HBM2e tiles. (Picture Credit: CNET)

This is Every part We Know About The 4th Gen Intel Sapphire Rapids-SP Xeon Household

In line with Intel, the Sapphire Rapids-SP will are available two package deal variants, an ordinary, and an HBM configuration. The usual variant will characteristic a chiplet design composed of 4 XCC dies that may characteristic a die measurement of round 400mm2. That is the die measurement for a singular XCC die and there might be 4 in complete on the highest Sapphire Rapids-SP Xeon chip. Every die might be interconnected through EMIB which has a pitch measurement of 55u and a core pitch of 100u.

The usual Sapphire Rapids-SP Xeon chip will characteristic 10 EMIB interconnects and all the package deal will measure at a mighty 4446mm2. Shifting over to the HBM variant, we’re getting an elevated variety of interconnects which sit at 14 and are wanted to interconnect the HBM2E reminiscence to the cores.

The 4 HBM2E reminiscence packages will characteristic 8-Hello stacks so Intel goes for at the very least 16 GB of HBM2E reminiscence per stack for a complete of 64 GB throughout the Sapphire Rapids-SP package deal. Speaking in regards to the package deal, the HBM variant will measure at an insane 5700mm2 or 28% bigger than the usual variant. In comparison with the just lately leaked EPYC Genoa numbers, the HBM2E package deal for Sapphire Rapids-SP would find yourself 5% bigger whereas the usual package deal might be 22% smaller.

- Intel Sapphire Rapids-SP Xeon (Normal Bundle) – 4446mm2

- Intel Sapphire Rapids-SP Xeon (HBM2E Bundle) – 5700mm2

- AMD EPYC Genoa (12 CCD Bundle) – 5428mm2

Intel additionally states that the EMIB hyperlink gives twice the bandwidth density enchancment and 4 occasions higher energy effectivity in comparison with normal package deal designs. Apparently, Intel calls the most recent Xeon lineup Logically monolithic which implies that they’re referring to the interconnect that’ll provide the identical performance as a single-die would however technically, there are 4 chiplets that might be interconnected collectively. You possibly can learn the total particulars relating to the usual 56 core & 112 thread Sapphire Rapids-SP Xeon CPUs right here.

Intel Xeon SP Households:

| Household Branding | Skylake-SP | Cascade Lake-SP/AP | Cooper Lake-SP | Ice Lake-SP | Sapphire Rapids | Emerald Rapids | Granite Rapids | Diamond Rapids |

|---|---|---|---|---|---|---|---|---|

| Course of Node | 14nm+ | 14nm++ | 14nm++ | 10nm+ | Intel 7 | Intel 7 | Intel 4 | Intel 3? |

| Platform Identify | Intel Purley | Intel Purley | Intel Cedar Island | Intel Whitley | Intel Eagle Stream | Intel Eagle Stream | Intel Mountain Stream Intel Birch Stream |

Intel Mountain Stream Intel Birch Stream |

| MCP (Multi-Chip Bundle) SKUs | No | Sure | No | No | Sure | TBD | TBD (Probably Sure) | TBD (Probably Sure) |

| Socket | LGA 3647 | LGA 3647 | LGA 4189 | LGA 4189 | LGA 4677 | LGA 4677 | LGA 4677 | TBD |

| Max Core Depend | Up To twenty-eight | Up To twenty-eight | Up To twenty-eight | Up To 40 | Up To 56 | Up To 64? | Up To 120? | TBD |

| Max Thread Depend | Up To 56 | Up To 56 | Up To 56 | Up To 80 | Up To 112 | Up To 128? | Up To 240? | TBD |

| Max L3 Cache | 38.5 MB L3 | 38.5 MB L3 | 38.5 MB L3 | 60 MB L3 | 105 MB L3 | 120 MB L3? | TBD | TBD |

| Reminiscence Help | DDR4-2666 6-Channel | DDR4-2933 6-Channel | Up To six-Channel DDR4-3200 | Up To eight-Channel DDR4-3200 | Up To eight-Channel DDR5-4800 | Up To eight-Channel DDR5-5600? | TBD | TBD |

| PCIe Gen Help | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 4.0 (64 Lanes) | PCIe 5.0 (80 lanes) | PCIe 5.0 | PCIe 6.0? | PCIe 6.0? |

| TDP Vary | 140W-205W | 165W-205W | 150W-250W | 105-270W | Up To 350W | Up To 350W | TBD | TBD |

| 3D Xpoint Optane DIMM | N/A | Apache Cross | Barlow Cross | Barlow Cross | Crow Cross | Crow Cross? | Donahue Cross? | Donahue Cross? |

| Competitors | AMD EPYC Naples 14nm | AMD EPYC Rome 7nm | AMD EPYC Rome 7nm | AMD EPYC Milan 7nm+ | AMD EPYC Genoa ~5nm | AMD Subsequent-Gen EPYC (Submit Genoa) | AMD Subsequent-Gen EPYC (Submit Genoa) | AMD Subsequent-Gen EPYC (Submit Genoa) |

| Launch | 2017 | 2018 | 2020 | 2021 | 2023 | 2023? | 2024? | 2025? |

Intel 7 Powered Ponte Vecchio GPUs For HPC

Lastly, now we have a terrific view of the Intel Ponte Vecchio GPU, the next-generation HPC answer. Ponte Vecchio was designed and created beneath the management of Raja Koduri who has been offering us with nice tidbits relating to the design philosophy and the insane compute energy which this chip packs.

Intel’s Ponte Vecchio is a gold mine of chiplets, housing over 47 completely different tiles on the identical package deal. (Picture Credit: CNET)

This is Every part We Know About The Intel 7 Powered Ponte Vecchio GPUs

Shifting over to Ponte Vecchio, Intel outlined some key options of its flagship knowledge middle GPU comparable to 128 Xe cores, 128 RT models, HBM2e reminiscence, and a complete of 8 Xe-HPC GPUs that might be linked collectively. The chip will characteristic as much as 408 MB of L2 cache in two separate stacks that may join through the EMIB interconnect. The chip will characteristic a number of dies primarily based on Intel’s personal ‘Intel 7’ course of and TSMC’s N7 / N5 course of nodes.

Intel additionally beforehand detailed the package deal and die measurement of its flagship Ponte Vecchio GPU primarily based on the Xe-HPC structure. The chip will consist of two tiles with 16 lively dies per stack. The utmost lively prime die measurement goes to be 41mm2 whereas the bottom die measurement which can also be known as the ‘Compute Tile’ sits at 650mm2. We’ve got all of the chiplets and course of nodes that the Ponte Vecchio GPUs will make the most of, listed beneath:

- Intel 7nm

- TSMC 7nm

- Foveros 3D Packaging

- EMIB

- 10nm Enhanced Tremendous Fin

- Rambo Cache

- HBM2

Following is how Intel will get to 47 tiles on the Ponte Vecchio chip:

- 16 Xe HPC (inside/exterior)

- 8 Rambo (inside)

- 2 Xe Base (inside)

- 11 EMIB (inside)

- 2 Xe Hyperlink (exterior)

- 8 HBM (exterior)

The Ponte Vecchio GPU makes use of 8 HBM 8-Hello stacks and accommodates a complete of 11 EMIB interconnects. The entire Intel Ponte Vecchio package deal would measure 4843.75mm2. Additionally it is talked about that the bump pitch for Meteor Lake CPUs utilizing Excessive-Density 3D Forveros packaging might be 36u.

The Ponte Vecchio GPU might be competing in opposition to NVIDIA and AMD HPC GPUs in 2023. (Picture Credit: CNET)

The Ponte Vecchio GPU is just not 1 chip however a mixture of a number of chips. It is a chiplet powerhouse, packing probably the most chiplets on any GPU/CPU on the market, 47 to be exact. And these are usually not primarily based on only one course of node however a number of course of nodes as we had detailed only a few days again.

Subsequent-Gen Knowledge Heart GPU Accelerators

| GPU Identify | AMD Intuition MI200 | NVIDIA Hopper GH100 | Intel Xe HPC |

|---|---|---|---|

| Flagship Product | AMD Intuition MI250X | NVIDIA H100 | Intel Ponte Vecchio |

| Packaging Design | MCM (Infinity Cloth) | MCM (NVLINK) | MCM (EMIB + Forveros) |

| GPU Structure | Aldebaran (CDNA 2) | Hopper GH100 | Xe-HPC |

| GPU Course of Node | 6nm | 5nm? | 7nm (Intel 4) |

| GPU Cores | 14,080 | 18,432? | 32,768? |

| GPU Clock Pace | 1700 MHz | TBA | TBA |

| L2 / L3 Cache | 2 x 8 MB | TBA | 2 x 204 MB |

| FP16 Compute | 383 TOPs | TBA | TBA |

| FP32 Compute | 95.7 TFLOPs | TBA | ~45 TFLOPs (A0 Silicon) |

| FP64 Compute | 47.9 TFLOPs | TBA | TBA |

| Reminiscence Capability | 128 GB HBM2E | 128 GB HBM2E? | TBA |

| Reminiscence Clock | 3.2 Gbps | TBA | TBA |

| Reminiscence Bus | 8192-bit | 8192-bit? | 8192-bit |

| Reminiscence Bandwidth | 3.2 TB/s | ~2.5 TB/s? | 5 TB/s |

| Type Issue | Twin Slot, Full Size / OAM | Twin Slot, Full Size / OAM | OAM |

| Cooling | Passive Cooling Liquid Cooling |

Passive Cooling Liquid Cooling |

Passive Cooling Liquid Cooling |

| TDP | This fall 2023 | 2H 2023 | 2023-2023? |

Intel’s Fab 42 is quickly anticipated to merge with the upcoming Fab 52 and Fab 62 within the coming years which might be producing what comes subsequent. Intel’s CEO, Pat Gelsinger, already broke floor on the Fabs again in September and that is the place you will note the manufacturing of the next-gen sub-Intel 7 merchandise.

Intel Course of Roadmap

| Course of Identify | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

|---|---|---|---|---|---|---|

| Manufacturing | In Excessive-Quantity (Now) | In Quantity (Now) | 2H 2023 | 2H 2023 | 2H 2024 | 2H 2025 |

| Perf/Watt (over 10nm ESF) | N/A | 10-15% | 20% | 18% | >20%? | TBA |

| EUV | N/A | N/A | Sure | Sure | Sure | Excessive-NA EUV |

| Transistor Structure | FinFET | Optimized FinFET | Optimized FinFET | Optimized FinFET | RibbonFET | Optimized RibbonFET |

| Merchandise | Tiger Lake | Alder Lake Sapphire Rapids Xe-HPG? |

Meteor Lake Granite Rapids Xe-HPC / Xe-HP? |

Lunar Lake? Diamond Rapids? TBA |

TBA TBA TBA |

TBA TBA TBA |

Information Supply: CNET