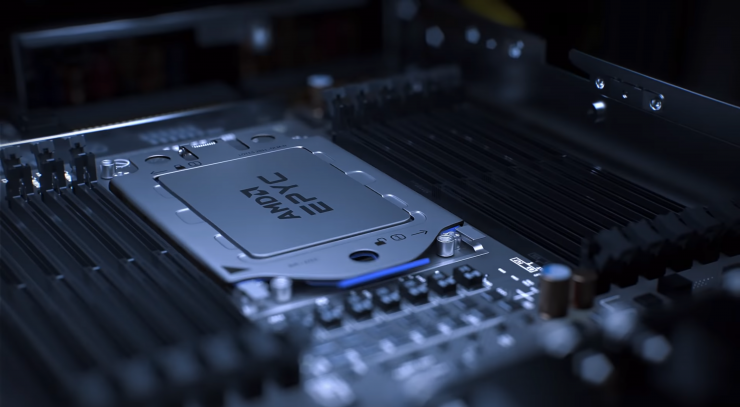

AMD’s next-generation EPYC Milan-X CPUs which is able to function 3D Chiplet packaging has leaked out by Momomo_US. The lineup will function an middleman answer earlier than the Zen 4 powered EPYC Genoa lineup arrives later in 2023-2023.

AMD’s EPYC Milan-X Server CPU SKUs Leak Out, Up To 64 Cores With 3D V-Cache Expertise?

AMD has thus far confirmed that it’s bringing 3D V-Cache chip stacking know-how to its Zen 3 core structure. The know-how would first be launched on next-generation Ryzen Desktop CPUs & from the appears of it, one other main product within the works with 3D V-Cache is Milan-X. AMD Milan-X has been identified for some time and will probably be just like present Milan EPYC 7003 CPUs besides they will get main modifications within the type of chiplet stacking.

EPYC 73○○X

(੭ु´・ω・`)੭ु⁾⁾— 188号 (@momomo_us) August 25, 2023

Following are the AMD EPYC 7003X Milan-X SKUs that had been leaked:

- EPYC 7773X 64 Core (100-000000504)

- EPYC 7573X 32 Core (100-000000506)

- EPYC 7473X 24 Core (100-000000507)

- EPYC 7373X 16 Core (100-000000508)

Curiously, all 4 SKUs listed right here retain the identical core counts as present variants so we aren’t going to see CCD upon CCD degree stacking so quickly. The CCDs retain their integral cache depend however will get a lift from the added SRAM cache by means of chiplet stacking.

Now what we all know concerning the 3D V-Cache know-how is that it’s achieved by means of the usage of Micro Bump (3D) & a number of TSV interconnects. The interconnect makes use of a model new hydrophilic Dielectric-Dielectric Bonding with Direct CU-CU bonding which was designed and co-optimized in partnership with TSMC. The 2 particular person silicons (chiplets) are bonded collectively utilizing this know-how. The 3D know-how options 9 Micron Pitch bonds.

A single 3D V-Cache stack would incorporate 64 MB of L3 cache that sits on high of the TSV’s already featured on present Zen 3 CCD’s. The cache will add upon the present 32 MB of L3 cache for a complete of 96 MB per CCD. AMD additionally said that the V-Cache stack can go as much as 8-hi which implies a single CCD can technically supply as much as 512 MB of L3 cache along with the 32 MB cache per Zen 3 CCD. So with a 64 MB of L3 cache, you’ll be able to technically rise up to 768 MB of L3 cache (8 3D V-Cache CCD stacks = 512 MB) which will probably be a mammoth improve in cache measurement.

3D V-Cache might simply be one facet of the EPYC Milan-X lineup. AMD may introduce sooner clocks as 7nm continues to mature and we are able to see a lot sooner efficiency from these stacked chips. It is usually attention-grabbing that the OPN codes for these processors are prepared which implies that a launch by late 2023 is very doubtless which might imply Milan-X could be the primary chip to introduce 3D V-Cache.

AMD EPYC CPU Households:

| Household Identify | AMD EPYC Naples | AMD EPYC Rome | AMD EPYC Milan | AMD EPYC Milan-X | AMD EPYC Genoa |

|---|---|---|---|---|---|

| Household Branding | EPYC 7001 | EPYC 7002 | EPYC 7003 | EPYC 7003X? | EPYC 7004? |

| Household Launch | 2017 | 2019 | 2021 | 2023 | 2023 |

| CPU Structure | Zen 1 | Zen 2 | Zen 3 | Zen 3 | Zen 4 |

| Course of Node | 14nm GloFo | 7nm TSMC | 7nm TSMC | 7nm TSMC | 5nm TSMC |

| Platform Identify | SP3 | SP3 | SP3 | SP3 | SP5 |

| Socket | LGA 4094 | LGA 4094 | LGA 4094 | LGA 4094 | LGA 6096 |

| Max Core Rely | 32 | 64 | 64 | 64 | 96 |

| Max Thread Rely | 64 | 128 | 128 | 128 | 192 |

| Max L3 Cache | 64 MB | 256 MB | 256 MB | 768 MB? | 384 MB? |

| Chiplet Design | 4 CCD’s (2 CCX’s per CCD) | 8 CCD’s (2 CCX’s per CCD) + 1 IOD | 8 CCD’s (1 CCX per CCD) + 1 IOD | 8 CCD’s with 3D V-Cache (1 CCX per CCD) + 1 IOD | 12 CCD’s (1 CCX per CCD) + 1 IOD |

| Reminiscence Assist | DDR4-2666 | DDR4-3200 | DDR4-3200 | DDR4-3200 | DDR5-5200 |

| Reminiscence Channels | 8 Channel | 8 Channel | 8 Channel | 8 Channel | 12 Channel |

| PCIe Gen Assist | 64 Gen 3 | 128 Gen 4 | 128 Gen 4 | 128 Gen 4 | 128 Gen 5 |

| TDP Vary | 200W | 280W | 280W | 280W | 320W (cTDP 400W) |